-晶体管逻辑电路,是一种基于双极结型晶体管(BJT)的数字逻辑电路技术。TTL电路因其高速、中小规模集成度和相对较低的成本而广泛应用于数字系统和计算机

随着半导体技术的发展,TTL电路已经经历了多代产品的迭代,从最初的TTL到低功耗的LTTL,再到高速的STTL,每一代都在性能和功耗方面进行了优化。

TTL电路的基本原理是建立在两个晶体管组成的开关电路上。输入端接收电压信号,通过一个NPN型晶体管传递到输出端的另一个PNP型晶体管,最终输出一定的电压水平,表示逻辑“1”或“0”。

当输入为高电平时,即逻辑“1”,NPN晶体管导通,使得PNP晶体管的基极电压降低,从而PNP晶体管截止,输出为高电平。

反之,当输入为低电平时,即逻辑“0”,NPN晶体管截止,PNP晶体管导通,输出为低电平。这种设计使得TTL电路具有快速响应和较强的驱动能力。

1.电源电压:TTL电路通常需要5V的直流电源供电。电源的稳定性对电路的性能至关重要。

2.输入阈值:TTL电路的输入阈值大约在1.4V左右,高于这个阈值的输入被认为是逻辑“1”,低于这个阈值的输入被认为是逻辑“0”。

3.输出电平:TTL电路的输出电平通常在3.5V以上为逻辑“1”,在1.5V以下为逻辑“0”。

4.扇出能力:这是指TTL电路能够驱动的标准负载数量。扇出能力取决于电路的设计和负载电容。

5.速度与功耗:TTL电路的速度和功耗是设计中需要平衡的两个因素。高速的TTL电路往往功耗较大,而低功耗的TTL电路速度较慢。

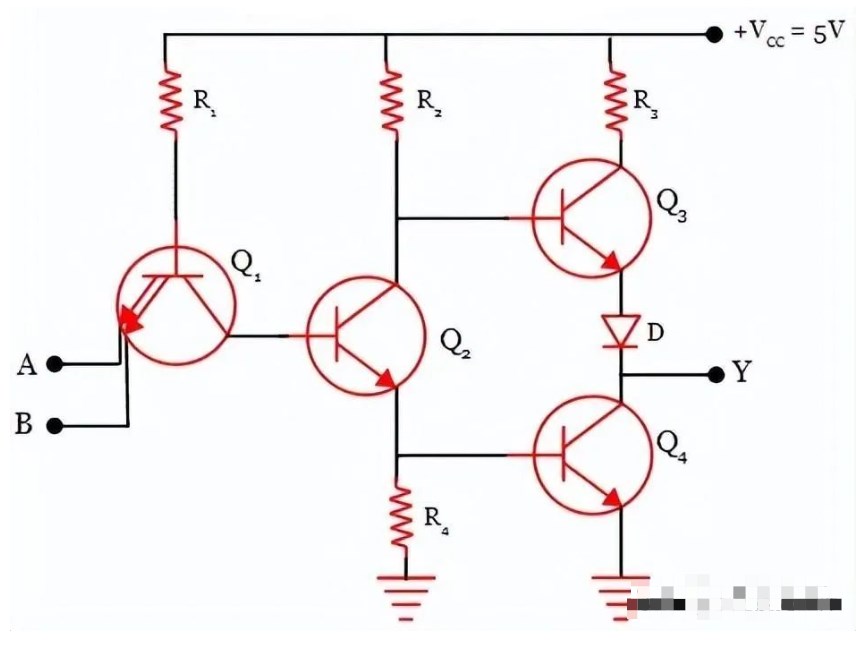

下图为2输入TTL与非门的电路图。它有四个晶体管Q 1、Q 2、Q 3和Q 4。

在发射极侧有两个输入端。三极管Q 3和Q 4组成输出端,称为图腾柱输出。

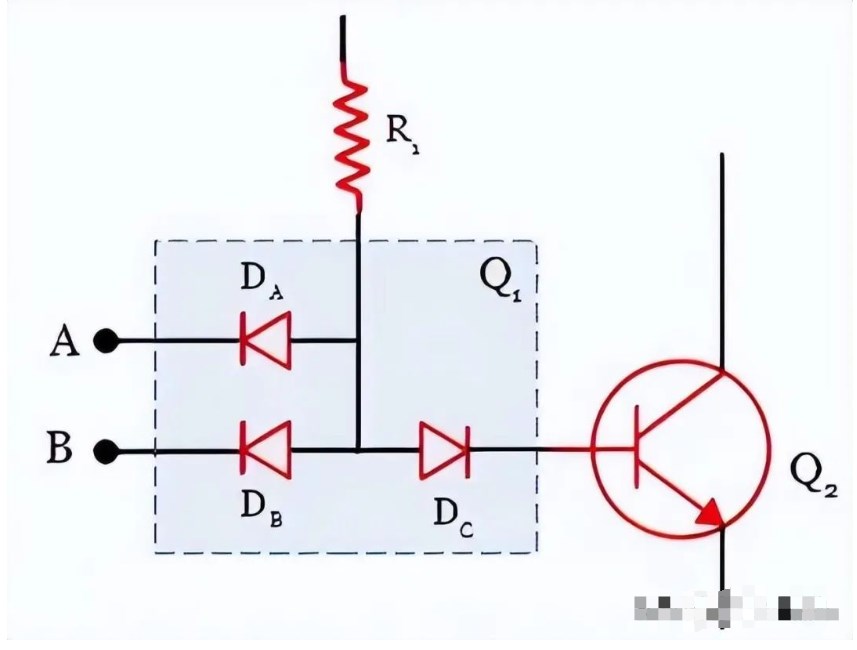

2 输入 TTL 与非门的电路可能看起来很复杂。我们可以通过考虑 2 输入 NPN 晶体管的

DC代表晶体管 Q2的集电极-基极结。当输入 A 和 B 均为低电平时,两个二极管均正向偏置。因此,由于电源电压 +V CC = 5 V 而产生的电流将通过 R 1 和两个二极管 D A 和 D B 流向地面。

电源电压在电阻R 1中下降 ,不足以导通晶体管 Q 2。随着 Q 2打开,晶体管 Q 4也将截止。但是晶体管Q 3被拉高。由于 Q 3是射极跟随器,因此

的输出也将为高电平,即逻辑 1。当任何一个输入(A 或 B)为低时,具有低输入的二极管将正向偏置。将发生与上述相同的操作,在这种情况下,输出将为高电平。

当输入 A 和 B 均为高电平时,发射极-基极结处的两个二极管都将反向偏置。集电极-基极结处的二极管 D C正向偏置。它将打开晶体管 Q 2。随着Q 2导通,晶体管Q 4也将导通。输出端的两个晶体管都将导通,因此终端输出将具有低电平,这被视为

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。举报投诉

,查看DWG格式的文件需要专用软件,当用AUTOCAD打开图纸,弹出对话框提示找不到字体时,建议一般选择hztxt.shx代替。

上灯具;另一种不规范做法:两个开关的动触点上都接入同一回路的相,零线,两个静触点上的出线都到灯具。双联双控开关

的方向吗? 我找到了连接到 Arduino 的说明,但很难将其转换为我的设备。

的可靠性。连接到高电平(Vcc)时,表示为逻辑高(1),连接到低电平(地/0V)时,表示为逻辑低(0)。如果

图解 /

艾为电子数字中功率音频功放 Digital Smart K Plus AW85825AW85828解读

求助:遇见诡异问题,FPGA模块A输出端口连接模块B输入后,模块A不能正常工作的

嵌入式设备在远端运行,会有偶发性代码跑飞的情况,无法到现场调试的情况下如何检查出问题?